# 38-GHz-Band High-Power MMIC Amplifier Module For Satellites On-Board Use

Masafumi Shigaki, *Member, IEEE*, Syoichi Koike, *Member, IEEE*, Kazuo Nogatomo, Kazuhiko Kobayashi, Hidenori Takahashi, Tetsuji Nakatani, Norio Tanibe, and Yoshiaki Suzuki

**Abstract**—This paper presents the design and development results of 38-GHz high-power MMIC amplifier modules for use in the solid state power amplifier (SSPA) to be carried aboard Engineering Test Satellite VI in 1993. This amplifier will be used in millimeter-wave inter-satellite communication experiments. For the development of this amplifier, we designed high-power, highly reliable FET's with 0.25  $\mu\text{m}$ -long gates. The FET large-signal impedance was accurately measured using an improved load-pull method and MMIC transformers. The measurements were used to design two types of MMIC's: one composed of two FET cells with 600  $\mu\text{m}$  wide gates, and the other of four FET cells with 400  $\mu\text{m}$  wide gates. We also developed a two-stage amplifier package consisting of two of these MMIC's that can be used at 38 GHz. We obtained a Po (1 dB) of 25 dBm and a gain of 11 dB. A 38-GHz test conducted during chip screening achieves a high production yield without circuits adjustment.

## I. INTRODUCTION

SINCE the first artificial satellite was launched in 1957, the launch of numerous communications, broadcast and observation satellites quickly followed. The increased traffic of communication has stimulated research and development of new satellite communications systems. Techniques under consideration include frequency reuse, land mobile satellite communications, and inter-satellite communications. In Japan millimeter-wave satellite communications experiments [1] are being planned under the aegis of the Ministry of Posts and Telecommunications Communications. These experiments will involve Engineering Test Satellite VI (ETS-VI), due for launch in 1993.

Technological improvement has steadily increased the power output and operating frequency of the solid-states power amplifiers (SSPA's) [2]–[6]. Today, the use of FET-based MMIC's at these frequencies has increased greatly [7]–[12]. Thus, it was planned to develop a millimeter-wave inter-satellite communications equipment, a specially developed on-board solid-state transponder. This

transponder will use SSPA having an output power of 0.5 W at 38 GHz.

This paper describes the development of an MMIC amplifier module for the last stage of the SSPA. The output power of this module is 0.3 W, and was increased to 0.5 W by combining two modules using a waveguide coupler. The purpose of this paper is to make a design method of millimeter-wave high-power MMIC amplifier for satellite on-board use. For realizing this purpose, we developed a new power FET, a large signal circuit design, and high-reliable production process.

In the first part of this paper, we describe the development of a high-performance FET with a 0.25  $\mu\text{m}$  long gate. To design the circuits, we needed to know FET's large-signal impedance at millimeter-wave frequencies. For this, we adopted a improved load-pull measuring method using MMIC transformers. This method and the experimental results will be discussed.

Two different MMIC's were used in the module in the final stage of the SSPA. One consisted of two FETs with 600  $\mu\text{m}$  wide gates, and the other consisted of four FET's with 400  $\mu\text{m}$  wide gates. This paper will describe the design and the characteristics of these MMIC's and the module using them. To aid in MMIC circuit design, we developed an accurate passive-circuit model useful up to 40 GHz. The module uses a hermetically sealed package for higher reliability and can be used at 38 GHz. The MMIC chips and modules were screened for use on board the satellite. All chips were tested at 38 GHz, and the test method and the results will be described.

## II. FET DESIGN

To develop a high-power FET for operation at 38 GHz, we developed a new FET process technology having the following features.

1. A tungsten silicide/gold (WSi/Au) gate structure, for improved reliability.

2. A mushroom-shaped gate structure, for higher frequency operation.

3. 0.25  $\mu\text{m}$ -long gates, for higher frequency operation.

4. Highly doped channels, for increased power.

5. A 50- $\mu\text{m}$  unit gate width, for increased gain.

Aluminium was used for the gate metal of the conventional FET's. This posses three problems. First, it is dif-

Manuscript received May 30, 1991; revised December 20, 1991.

M. Shigaki, H. Takahashi, T. Nakatani, and N. Tanibe are with Fujitsu Ltd., 1015 Kamikodanaka, Nakahara-ku, Kawasaki 211, Japan.

S. Koike, K. Nogamato, and K. Kobayashi are with Fujitsu Laboratories, Ltd., 1015 Kamikodanaka, Nakahara-ku, Kawasaki 211, Japan.

Y. Suzuki is with Communications Research Laboratories, Ministry of Posts and Telecommunications, 2-1, Nukui-Kitamachi, 4-chome, Koganei-shi, Tokyo 184, Japan.

IEEE Log Number 9107705.

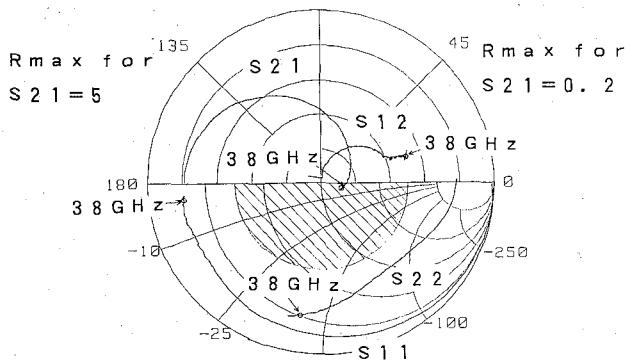

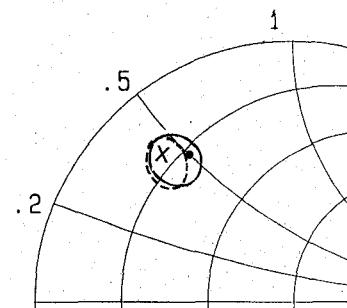

Fig. 1.  $S$  parameters of FET with 400- $\mu\text{m}$ -wide, and 0.25- $\mu\text{m}$  long gates. The bias conditions are  $V_{ds} = 8$  V,  $V_{gs} = 0.94$  V,  $I_{ds} = 57.9$  mA. The frequency is from 45 MHz to 40 GHz. Small closed circles represent at 38-GHz data. The hatched area shows the tuner's coverage area viewed from the FET at 38 GHz. The area is not covered the input and output impedance of the FET.

ficult to get a mushroom-shaped gate structure with aluminium. Second, aluminium's migration is about  $10^5$  A/cm $^2$ . This reduces the reliability of a high-power FET. Third, gate resistance increases as the gate length is reduced. This degrades the high-frequency performance. To solve these problems, we used a WSi/Au gate structure and gold to achieve the mushroom-shaped gate. This increases the migration to  $10^6$  A/cm $^2$ , and improves reliability because grain size of WSi is smaller than that of aluminium.

When the gate length is shortened, the thin highly-doped channel is need. Therefore, we used a thin highly-doped channel ( $3.5 \times 10^{17}$  cm $^{-3}$ ). To determine if there are any problems associated with this channel, we also fabricated a normally-doped channel FET ( $1.7 \times 10^{17}$  cm $^{-3}$ ) and compare the characteristics. The results of this investigation showed that the  $gm$  of the highly-doped FET is 20 mS larger, its  $C_{gs}$  is larger, its  $G_a(\text{max})$  at 26.5 GHz is 1.2 dB higher, and its drain leakage current at the pinch-off voltage is lower than that of the normally-doped FET with a 600  $\mu\text{m}$  wide gate. Thus, there are no problems even if a highly doped epitaxial wafer is used.

The unit gate width was investigated at this time because this FET would be used at millimeter-wave frequencies. For this purpose, we fabricated and compared the characteristics of FET's having 50- and 75- $\mu\text{m}$  unit gate widths. The overall gate width of both FET's was 600- $\mu\text{m}$  (50- $\mu\text{m}$   $\times$  12, or 75- $\mu\text{m}$   $\times$  8). The  $G_a(\text{max})$  of the 50- $\mu\text{m}$  unit gate width FET was 0.7 dB higher. Thus the 50- $\mu\text{m}$  unit gate width was chosen.

After further study, FETs with 400- $\mu\text{m}$  and 600- $\mu\text{m}$  gate widths were developed for the MMICs to be used in the final stage of the SSPA. The  $S$ -parameter measurement of the FET with 400- $\mu\text{m}$  gate width are shown in Fig. 1. To measure  $S$ -parameters, the FET's were secured to a metal carrier to ensure that the thermal conditions under test were the same as those in the amplifier. The  $G_a(\text{max})$  at 38 GHz for the FET's 400- $\mu\text{m}$ -wide gates was 5 dB, and 6 dB for the FET's with 600- $\mu\text{m}$ -wide gates.

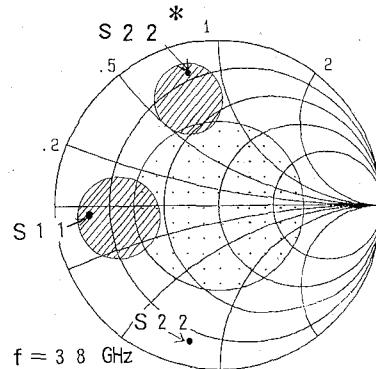

Fig. 2. Impedance coverage viewed from the FET using an external tuner. Dotted area represent for direct connection to the tuner. Closed circles represent MMIC impedance transformer use.

### III. IMPROVED LOAD-PULL MEASUREMENTS

Large-signal impedance matching is required [13] because the MMIC is a high-power amplifier. Measurement of the large-signal impedance of a FET operating at millimeter-wave frequencies is difficult for the following reasons:

1) The large-signal impedance can be accurately measured using an RF wafer probe, and a tuner [14]. However, the tuner's coverage as viewed from the FET cannot cover the optimum input-output impedance position in the neighborhood of the FETs matching impedance  $S$ -parameter conjugate as shown in Figs. 1 and 2. This is because the impedance of  $S_{11}$  and  $S_{22}$  of the FET is low in the millimeter-wave band, and because there is a large loss between the FET and the tuner.

2) An MIC tuner near the FET prevents loss, but the bonding wires between the tuner and FET vary in length, making accurate measurement difficult.

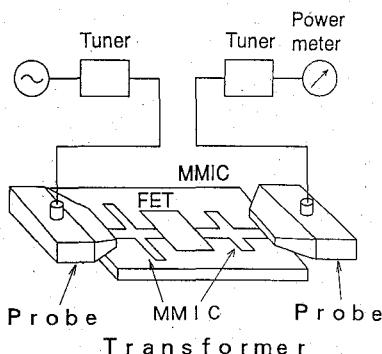

To solve these problems, we used an MMIC impedance transformer to convert the tuner's coverage area to that shown by the hatched area in Fig. 2. This area includes the conjugate matching impedance of the FET. The measuring system shown in Fig. 3. can measure the large-signal impedance accurately because it uses no bonding wires and uses a wafer probe to measure impedance. The MIC transformer converts the tuner coverage to a small area as viewed from the FET even if the tuner's reproducibility is somewhat low. This greatly improves measurement accuracy. To calculate the impedance as viewed from the FET, the MMIC matching circuit must be evaluated accurately. Therefore, we measured the matching circuit separately.

A few problems remain to be solved. First, when the tuner is operated, vibration is transmitted to the MMIC through the probe, shifting the contact point of the probe. This problem was solved by separating the probe from the MMIC when the tuner is operated. The MMIC transformer keeps the reproducibility error due to re-contact below 1° as viewed from the FET, so no measurement problem is raised. Second, there is loss between the MMIC transformer and the tuner, so the output power

Fig. 3. Impedance measurement system using an MMIC impedance transformer.

rapidly drops as the tuner's impedance goes into the high VSWR region. Therefore, we didn't use the tuner in the high VSWR region. For this reason, we can research only a small hatched area as shown in Fig. 2. Even so, this impedance conversion method can realize a high impedance as viewed from the FET. And no problem arise because the optimum large-signal impedance is in the neighborhood of conjugate impedance of the FET *S*-parameter.

We designed and produced two types of FET, one with 400- $\mu\text{m}$ -wide gates, and the other with 600- $\mu\text{m}$ -wide gates. Each FET with MMIC transformer has a maximum gain at a frequency of about 33 GHz, indicating that the FET's and transformers were designed properly.

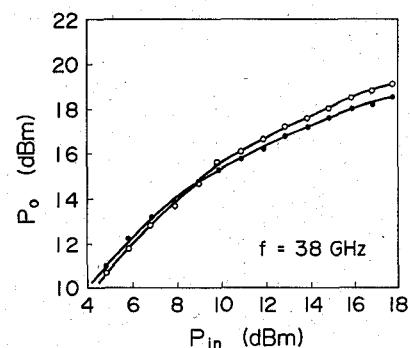

Fig. 4 shows the results of measurement of the FET's with 400- $\mu\text{m}$ -wide gates. The maximum output power was 10.8 dBm and the gain was 6.1 dB when the input power was 4.7 dBm. The maximum output power and the gain were also obtained 16.2 dBm and 6.2 dB when the input power was 10 dBm, and 17.35 dBm and 4.35 dB when the input power was 13 dBm, respectively. The phase angle of the optimum impedance increases with input power. These results agree with actual experience. When the input power is high, the equivalent output power circle 1 dB down from the maximum output point tends to grow, indicating how output saturation progresses. In Fig. 5 the input-output characteristics at the optimum impedance were measured at input powers of 4.7 dBm. The difference is about 0.5 dB at saturation.

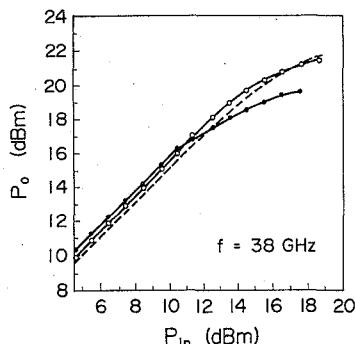

Fig. 6 shows the results of measurement of the FET's with 600  $\mu\text{m}$  wide gates. The phase angle of the optimum impedance increases with increased input power, as with the FET with 400  $\mu\text{m}$  wide gates. This result agrees with the optimum impedance position [11] measured using the equivalent load-pull method. The input-output characteristics at the optimum impedances were measured at input powers of 6 dBm and 16 dBm as shown in Fig. 7. The characteristic of the input power 6 dBm is considered small signal matching, and that of the input power 16 dBm is considered large signal matching. Thus, the results show that small signal matching case has higher gain when the input power below 11 dBm, and large signal matching case has higher gain when input power exceed 11 dBm.

Fig. 4. Equal-power loci for a FET with 400- $\mu\text{m}$ -wide gate measured at 38 GHz. The closed circle, cross, and triangle shows the maximum output power impedance, when an input powers are 4.7 dBm, 10 dBm, and 13 dBm, respectively. The output powers are 10.8 dBm, 16.2 dBm, 17.35 dBm, respectively. The solid line, broken line, dotted line circles represent the equivalent output power circule 1 dB down from each maximum output power.

Fig. 5. Input and output power characteristics of a FET with 400- $\mu\text{m}$ -wide gate. The closed circles characteristics are obtained when the output matching circuit impedance is adjusted to obtain the maximum output power at an input power of 4.7 dBm (the closed circle impedance position in the Fig. 4). The open circles characteristics are obtained when the output impedance is adjusted to obtain the maximum output power at an input power of 10 dBm (triangle impedance position in Fig. 4).

Fig. 6. Equal-power loci for a FET with 600- $\mu\text{m}$ -wide gate, measured at 38 GHz. The closed circle, and cross shows the maximum output power impedance, when an input powers are 6 dBm, and 16 dBm, respectively. The output powers are 9.3 dBm, and 20.1 dBm, respectively. The solid line, broken line circles represent the equivalent output power circle 1 dB down from each maximum output power.

The difference between the characteristics was 1.5 dB when the input power was 17.5 dBm. Other chip was mounted on a metal carrier, and MIC circuit was connected outside the chip, then the circuit was adjusted so that the maximum output was obtained at 16 dBm input power. The input-output characteristics of the chip agreed

Fig. 7. Input and output power characteristics of a FET with 600- $\mu$ m-wide gate. The closed circles characteristics are obtained when the output matching circuit impedance is adjusted to obtain the maximum output power at an input power of 6 dBm (the closed circle impedance position in the Fig. 6). The open circles characteristics are obtained when the output impedance is adjusted to obtain the maximum output power at an input power of 16 dBm (cross impedance position in the Fig. 6). The broken line shows the characteristics of a chip using an MIC tuner to obtain the highest power when the input power is 16 dBm.

with the data using this method as shown in Fig. 7. This shows that this measurement method is reliable.

#### IV. MMIC AMPLIFIER DESIGN

The two-stage amplifier consists of two different MMICs: the names are FLR056XV/ETS and FLR066XV/ETS. FLR056XV/ETS consists of two FET's with 600- $\mu$ m-wide gates, and FLR066XV/ETS consists of four FETs with 400- $\mu$ m-wide gates. FLR056XV/ETS is used in the driver stage, and FLR066XV/ETS is used in the last stage.

The in-phase combiner circuits was used for reducing the chip size. Large-signal circuit design using in-phase combiners was a problem. When we design a amplifier without in-phase combiner, the optimum impedance viewed from the FET is easily realized. Because the output impedance viewed from the FET can be known by calculating the passive output matching circuit. In a combined circuit, however, the impedance viewed from the FET can be obtained only when the other FET is operating. If an attempt is made to measure the impedance of a terminal by removing one FET, the balance of the combined circuit is lost and the impedance cannot be measured correctly. In an in-phase combined circuit, connecting the ports operating in parallel with a zero-length line does not affect operation. Therefore, the output circuit terminals connecting with the FET's were stlaped by a zero-length line, and we calculated the impedance of the output circuits. But the characteristic impedance viewed from the FET terminals was 12.5  $\Omega$  for the four FETs combiner case. The impedance was converted to 50  $\Omega$  system by connecting an ideal transformer. The impedance viewed from here is equal to that viewed from one FET operating in parallel. We used this ideal transformer when the circuit was designed.

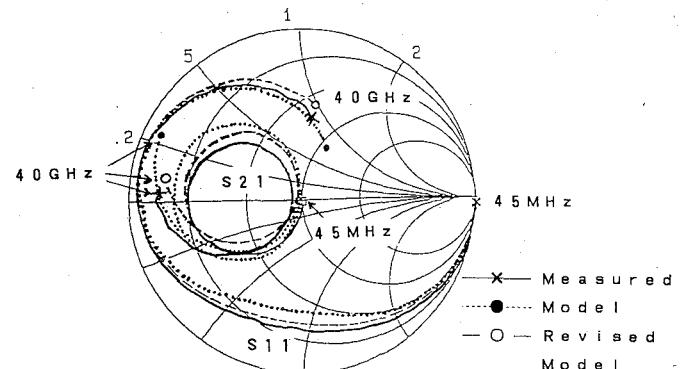

Circuit calculations were based on Touchstone program version 1.7. This passive circuit model is guaranteed for

Fig. 8. Impedance loci of a matching circuit, measured from 45 MHz to 40 GHz. The solid, dotted line, and broken line are the measured data, data from the equivalent circuit model using Touchstone version 1.7, and data from the modified equivalent circuit model, respectively.

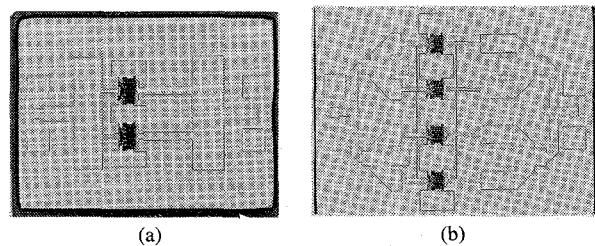

Fig. 9. (a) Photographs of the FLR056XV/ETS chip, which is composed of two FET cells with 600  $\mu$ m wide gates. The chip measures 1.35  $\times$  1.8 mm. (b) Photographs of the FLR066XV/ETS chip, which is composed of four FET cells with 400  $\mu$ m wide gates. The chip measures 1.55  $\times$  1.95 mm.

frequencies up to 20 GHz. Furthermore, our circuit is fabricated on a GaAs substrate. Therefore, the programs passive circuit model was modified and used. The circuit is a combined circuit consisting of multiple FET's. Therefore, each input and output passive circuit was looped at the FET and a single test terminal provided for each circuit. Three different line length patterns were fabricated to the correct the passive model. In the passive circuit of the FLR056XV/ETS, the effective line width 5% to 10% thinner than the actual pattern. In the case of the FLR066XV/ETS pattern, we found that, 120- and 140- $\mu$ m-wide lines are 40% thinner than the actual pattern. Fig. 8 shows an example.

For the FLR066XV/ETS, oscillation was prevented by inserting an oscillation prevention circuit in the neighborhood of the FET, as shown in Fig. 9(b). This circuit consist of the thine line by straping the ports operating in parallel. For RF inspection of all chips, co-planar lines were used for input and output.

#### V. MMIC PERFORMANCE

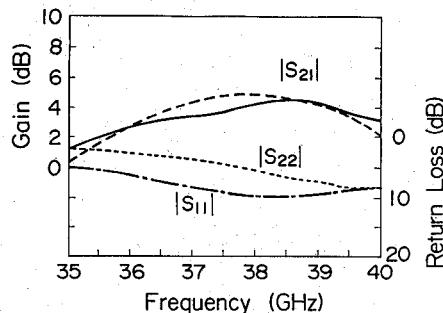

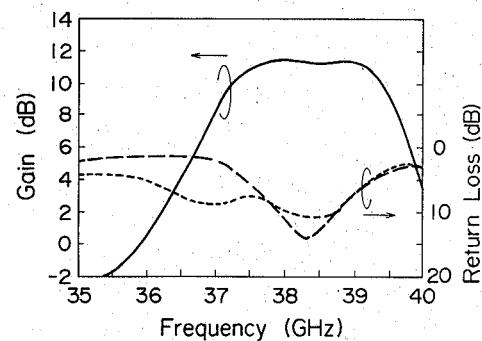

Fig. 9 shows the fabricated chips. The FLR056XV/ETS measures 1.35  $\times$  1.85 mm and FLR066XV/ETS 1.55  $\times$  1.95 mm. As described in the preceding section, these MMICs can be measured with an RF wafer probe. Fig. 10 shows the typical gain characteristics of a FLR066XV/ETS mounted on the metal carrier. The characteristics agree with the calculations.

Fig. 10. Typical frequency characteristics of the FLR066XV/ETS on a metal carrier. The broken line represents the predicted characteristics. Other lines are data measured using an RF wafer probe.

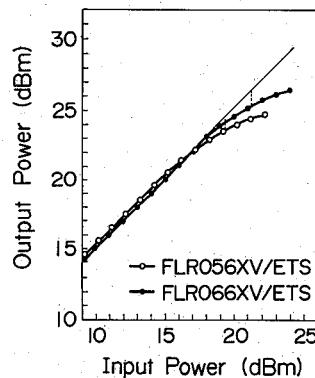

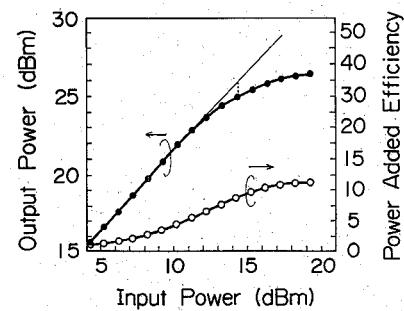

Fig. 11. Input and output characteristics of the FLR056XV/ETS and FLR066XV/ETS measured using a test fixture.

The chip was secured to a metal carrier and its characteristics measured (Fig. 11). The gain,  $P_o$  (1 dB), and efficiency of the FLR056XV/ETS were 5.4 dB, 23.5 dBm, and 12%, and 5.1 dB, 25.2 dBm, and 11% for the FLR066XV/ETS. The temperature characteristic from  $-10^{\circ}\text{C}$  to  $50^{\circ}\text{C}$  was  $0.028 \text{ dB} / ^{\circ}\text{C}$  for the FLR056XV/ETS and  $0.023 \text{ dB} / ^{\circ}\text{C}$  for the FLR066XV/ETS.

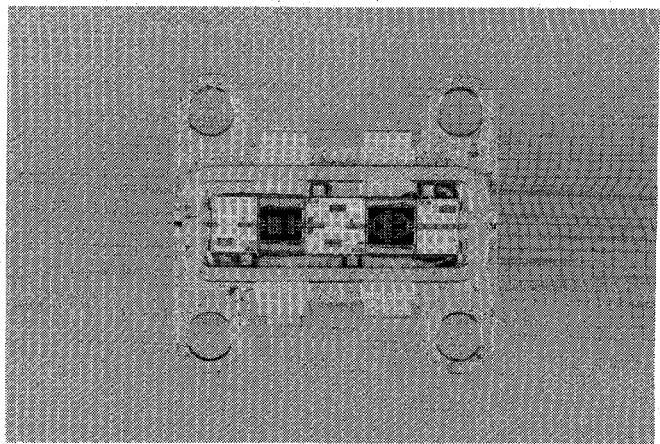

## VI. AMPLIFIER MODULE DESIGN AND PERFORMANCE

A module consisting of two stages (first stage: FLR056XV/ETS, second stage: FLR066XV/ETS) sealed in a package was designed and fabricated. Sealing was used to control module reliability and to improve the module's environmental resistance. The module was to operate at a high frequency (38 GHz), so a  $3 \times 10 \times 1 \text{ mm}$  cavity was selected. The package can prevent wave-guide-mode resonances up to 45 GHz. The RF terminals consist of sealed micro-strip lines, and the transmitting loss of a terminal is 0.2 dB. Four dc terminals extend vertically downward and a low-pass filter to cut off the RF signal is incorporated into the terminal passage. The package base is copper, so the thermal resistance is low, but the thermal expansion rate is two times that of GaAs. Therefore, a chip base made of a copper-tungsten alloy was inserted under the MMIC to reduce stress during die bonding. A dc blocking and a bias circuit were provided between boards connecting the MMIC's.

Fig. 12. Photograph of the module.

Fig. 13. Typical module frequency characteristics.

Fig. 14. Typical module input and output characteristics.

Figs. 12 to 14 show the fabricated module. A gain exceeding 11 dB was obtained over a wide band (1.5 GHz) from 37.5 GHz to 39.0 GHz at room temperature.  $P_o$  (1 dB) and  $P_o$  (sat) were 25.0 dBm and 26.5 dBm. The power-added efficiency was 12%, and the temperature characteristic of the module was  $0.074 \text{ dB} / ^{\circ}\text{C}$  from  $-10^{\circ}\text{C}$  to  $50^{\circ}\text{C}$ .

## VII. AMPLIFIER MODULE SCREENING FOR QUALITY ASSURANCE

Developed as a module to be used aboard the ETS-VI satellite, the amplifier module was manufactured in processes grounded on reliability assurance. This is the first millimeter-wave-band MMIC to be used in the satellite.

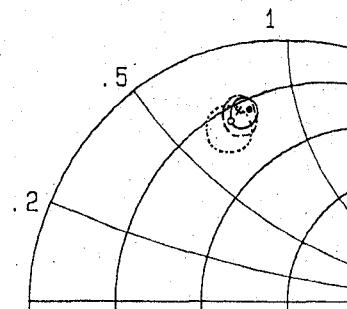

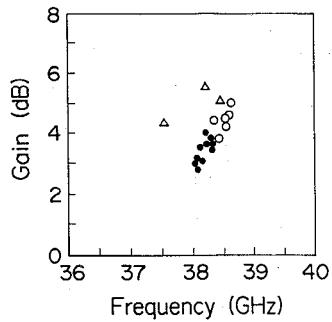

In this screening process, we adopted RF probe test to the MMIC chip. This is the first RF probe test in millimeter-wave frequencies. Namely, after dc and wafer pilot tests, the gain characteristics of all chips to be shipped are checked at 38 GHz. Because the characteristic in the 38-GHz band cannot be presumed from the DC characteristics. This process can ensure the final characteristics of the assembled modules. Mounting a chip in a package changes the thermal condition of the chip and the bonding wire effects of the RF characteristic. Therefore, the specification for screening test in chip measurement was established by measuring how the characteristics of a chip are affected by mounting it. Fig. 15 shows how the FLR066XV/ETS characteristics change. From this data, the specification of RF probe test was determined. Of 242 FLR056XV/ETS devices tested, 190 were acceptable, the average gain was 4.87 dB, and the variation in gain was 0.27 dB. Of 218 FLR066XV/ETS devices tested, 153 were acceptable, the average gain was 3.18 dB, and the variation in gain was 0.21 dB. The RF inspection reduces RF characteristic variation, thus increasing the yield in subsequent assembly tests.

Following screening tests were also done, temperature cycling (-55 to 125°C, 30 min., 25 cycle), Mechanical shock test (1500 G, 0.5 mS, Y1, once), Constant acceleration (5000 G, Y1, 1 min, once), PIND (60 Hz, 20 G), dc burn-in ( $T_j = 90\%$ , 168H), and so on.

The average pinch-off voltage was 2.6 V, and the variation was about 100 mV. The average bond pull strength of the MMIC's was a 3.83 g (specification: 2.5 g). The yield is estimated to be 87.3%. The average die shear strength was 3939 g. The probability that this strength will exceed the specification (1680 g) is 98.5%.

In the module assembly test, internal circuits were not adjusted because such a process generates fine dust such as scrap metal which may lower the yield in the PIND test. In the RF test of the modules, measuring jigs were kept in good condition, and it was confirmed before and after the test that the return loss was at least 15 dB. The gate current  $I_g$ (RF) was measured with saturated output, and the life of the MMIC was estimated from the  $I_g$ . The bias of the amplifier was designed so that  $I_g$ (RF) is small when the module is mounted. The limiter resistance to the gate current was inserted to the bias circuit.

Modules were burned-in twice to observe the change in DC characteristics and to locate problems. The RF characteristic was not checked in the intermediate test, because inserting the module into a jig causes the linear gain to change slightly (about 0.5 dB), and it is difficult to check whether the RF characteristic truly changed.

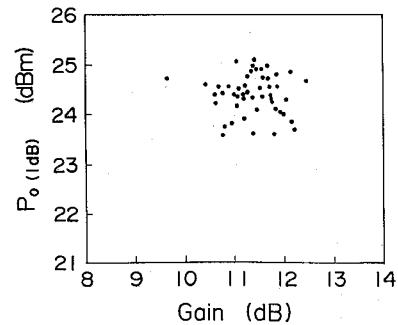

Fig. 16 shows an example of module characteristics in the final test of 49 modules. The gain was 10.5 dB to 12.5 dB. The output level was 23.5 dB to 25 dB. As mentioned earlier, the gain and output level changed little even though modules were not adjusted. This indicates that the RF inspection of the chips was effective.

Fig. 15. Gain and peak frequency characteristics of the FLR066XV/ETS. The solid circles represent bare chip measurement using RF wafer probe. The open circles represent measurement using an RF wafer probe with the chip mounted on a metal carrier. The open triangles represent measured by using a test fixture.

Fig. 16. Module gain and output power measured at 1-dB gain compression at final electrical test.

Three modules were selected for use in the SSPA's to be used on board the ETS-VI. Others were kept as spares, for testing, for confirming reliability, and for checking module reliability. The failure rate of the modules to be used is given by

$$\lambda_p = [\Sigma N_C \lambda_C \Pi_C + (N_R \lambda_R + \Sigma N_1 \lambda_1 + \lambda_S) \cdot \Pi_F \Pi_E] \Pi_Q \Pi_D \quad (1)$$

where  $\lambda_p$ : failure rate ( $10^{-6}/\text{hour}$ ),  $N_C$ : stress coefficient,  $\lambda_C$ : failure rate of the MMIC,  $\Pi_C$ : acceleration coefficient,  $N_R$ : number of film resistors,  $\lambda_R$ : failure rate of film resistor,  $N_1$ : number of connection points,  $\lambda_1$ : Failure rate of the interconnection,  $\lambda_S$ : failure rate of the package,  $\Pi_F$ : environment coefficient,  $\Pi_Q$ : quality efficiency, and  $\Pi_D$ : mounting density. If the temperature changes from  $-25^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $\lambda_p$  is estimated to be  $0.2888 \times 10^{-6}/\text{hour}$  (288.8 FIT) or less. Now, temperature accelerated test is done for estimating module life.

### VIII. CONCLUSION

We have developed MMIC amplifier modules to be used in the 38-GHz SSPA for a millimeter-wave inter-satellite communications device to be carried on board the ETS-VI satellite. FET's with  $0.25\text{-}\mu\text{m}$ -long gates and a highly doped epitaxial layer (carrier density:  $3.5 \times 10^{17} \text{ cm}^{-3}$ )

were developed for use in these MMIC's. A WSi/Au gate metal structure was used for high reliability. The large signal impedance of the FET at 38 GHz was measured with an improved load-pull method using an MMIC transformer. This method converts tuner impedance coverage as viewed from the FET to the neighborhood of the conjugate impedance of the FET S-parameter. Impedance conversion reduces the variations in the FET. This method was used to measure the large-signal impedance of FETs with 600- $\mu$ m and 400- $\mu$ m-wide gates. The passive circuit was measured at frequencies up to 40 GHz and a highly precise passive circuit was produced by modifying the 20-GHz Touchstone circuit model. As a result the obtained characteristics were almost as designed. The gain and Po (1 dB) of four combined FET's were 4.5 dB and 25.1 dBm. A strip line interface package that can be used at 38 GHz was developed, and the two-stage MMIC amplifier sealed in it. The gain and Po (1 dB) of the amplifier were 11 dB and 25 dBm. Screening of chips to be used on board the satellite was done to ensure reliability. RF inspection of the MMIC chips increased the yield in mass production.

#### REFERENCES

- [1] T. Iida, S. Shimoseko, K. Iwasaki, and M. Shimada, "On future missions of satellite communications," in *Proc. 14th Int. Symp. on Space Technology and Science*, 1984, pp. 22-33.

- [2] B. Dornan, M. Cummings, and F. McGinty, "Advances in the design of solid-state power amplifiers for satellite communications," *RCA Rev.*, vol. 45, pp. 619-630, 1984.

- [3] S. S. Mochalla, D. E. Aubert, "20-GHz lumped-element GaAs FET driver amplifier," *RCA Rev.*, vol. 45, pp. 670-680, 1984.

- [4] P. M. Smith *et al.*, "A 0.15  $\mu$ m gate-length pseudomorphic HEMT," in *1989 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 983-986.

- [5] H. Nakashima and N. Mita, "A high-efficiency and 3 W output on board solid state power amplifier in 20 GHz band," in *1990 Spring National Convention Rec.*, pp. 2-208.

- [6] H. Barth and M. Pirk, "A 2 W solid state transmitter for short range data communication at 60 GHz," in *1990 IEEE MTT-S Microwave Symp. Dig.*, pp. 931-933.

- [7] F. S. Auricchio, "12-W 20-GHz GaAs FET power amplifier with 15.5% power-added efficiency," in *1989 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 3, pp. 933-936.

- [8] G. Hegazi *et al.*, "GaAs molecular beam epitaxy monolithic power amplifier at U-band," in *1989 IEEE MTT-S Microwave Symp. Dig.*, pp. 209-213.

- [9] K. Seino, Y. Imai, M. Kobiki, and T. Takegi, "A 28 GHz band high power FET amplifier," in *Proc. 3rd Asia-Pacific Microwave Conf.*, pp. 549-552.

- [10] M. Muraguchi and M. Nakatsugawa, "A 26 GHz-band uniplanar MMIC amplifier using series and parallel divider/combiner combination technique," in *1991 Autumn National Convention Rec.*, pp. 2-504.

- [11] G. Toyoshima, K. Seino, T. Takagi, Y. Imai, and S. Urasaki, "Ka-band 1 W monolithic directly connected 2-stage amplifier," in *1991 Spring National Convention Rec.*, pp. 2-507.

- [12] S. Arai, H. Kojima, K. Otuka, M. Kawano, S. Watanabe, H. Ishimura, and H. Tokuda, "Millimeter-wave power HEMT," in *1991 Spring National Convention Rec.*, pp. 2-508.

- [13] R. R. Pantoja, M. J. Howes, J. R. Richardson, and C. M. Snowden, "A large-signal physical MESFET model for computer-aided design and its applications," *IEEE Trans. Microwave Theory Tech.*, vol. 37, no. 12, pp. 2039-2045, 1989.

- [14] W. R. Curtice, P. Pak, "On-wafer verification of a large-signal MESFET model," *IEEE Trans. Microwave Theory Tech.*, vol. 37, no. 11, pp. 1809-1811, 1989.

**Masafumi Shigaki** (M'87) was born in Hyogo, Japan, on October 4, 1952. He received the B.S. and M.S. degrees in electrical engineering from Hokkaido University, Sapporo, Japan, in 1975 and 1977, respectively.

He joined Fujitsu Laboratories Ltd., Kawasaki, Japan, in 1977, and since then has been engaged in research on microwave integrated circuits and GaAs monolithic integrated circuits. In 1990, he joined Fujitsu Ltd., where he worked on the development of space and satellite communication equipment. He is presently a Section Manager in the space technology development group.

Mr. Shigaki is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Shoichi Koike** (M'87) was born in Hokkaido, Japan, February 21, 1959. He received the B.E. degree in electrical engineering from Yamanashi University, Kofu, Japan, in 1981, became a Research Student at the same university, and later received the M.E. and D.E. degrees in electrical engineering from Hokkaido University, Sapporo, Japan, in 1984 and 1987, respectively. He presently is engaged in the Radio and Satellite Communication Systems Laboratory at Fujitsu Laboratories Ltd., Kawasaki.

Dr. Koike is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Kazuo Nagatomo**

**Kazuo Nagatomo** was born in Kyoto, Japan, in 1962. He received the B.E. degree in electric engineering from National Defense Academy, Yokosuka, Japan, in 1986.

In 1986 he joined Fujitsu Laboratories Ltd., Kawasaki, Japan, as an Engineer in the Radio and Satellite Communication Systems Laboratory, and has been engaged in research and development of MMIC's.

He is a member of the Institute of Electronics, Information and Communication Engineers of

**Kazuhiko Kobayashi** was born in Nagano, Japan on February 23, 1963. He received the B.S. and M.S. degrees in electronics engineering from Nihon University, Chiba, Japan, in 1985, and 1987, respectively.

In 1987 he joined Fujitsu Laboratories Ltd., Kawasaki, Japan. From 1987 to 1991, he was engaged in the research and development of satellite communication systems. Since 1991, he has been working on the development of radio equipment for digital mobile communication systems.

**Hidenori Takahashi** was born in Oita, Japan, on December 2, 1961. He graduated from Fujitsu Technical High School in 1984. Presently, he is with Compound Semiconductor Division, Fujitsu Limited.

**Norio Tanibe** was born in Hiroshima, Japan, in 1945.

He joined Fujitsu Limited in 1963, where he has been engaged in the research and development of microwave circuits.

**Tetsuji Nakatani** was born in Nara, Japan, in 1952.

In 1971, he joined Fujitsu Limited, where he has been engaged in the research and development of microwave circuits.

**Yoshiaki Suzuki** was born in Sendai, Japan, on November 30, 1951. He received the B.S. and M.S. degrees in electrical engineering from Tohoku University, Sendai, Japan, in 1974 and 1976, respectively.

Since 1976, he has been working in the Communications Research Laboratory, Ministry of Posts and Telecommunications, and has been engaged in research on satellite communication. His current interest includes millimeter wave satellite communication system.

Mr. Suzuki is a member of the Institute of Electronics, Information and Communication Engineers of Japan.